Product Summary

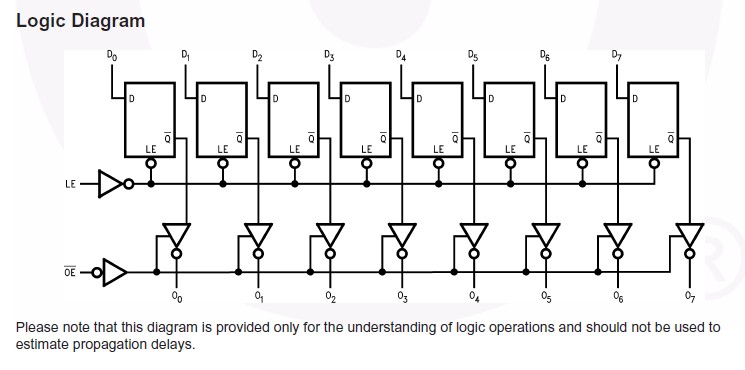

The 74ABT573CPC is an octal latch with buffered common Latch Enable (LE) and buffered common Output Enable (OE) inputs. This device is functionally identical to the ABT373 but has broadside pinouts. The 74ABT573CPC contains eight D-type latches with 3-STATE output buffers. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches of the 74ABT573CPC are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW the latches store the information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE. The 3-STATE buffers of the 74ABT573CPC are controlled by the Output Enable (OE) input. When OE is LOW, the buffers are in the bi-state mode. When OE is HIGH the buffers are in the high impedance mode but this does not interfere with entering new data into the latches.

Parametrics

74ABT573CPC absolute maximum ratings: (1)TSTG, Storage Temperature: –65℃ to +150℃; (2)TA, Ambient Temperature Under Bias: –55℃ to +125℃; (3)TJ, Junction Temperature Under Bias: –55℃ to +150℃; (4)VCC, VCC Pin Potential to Ground Pin: –0.5V to +7.0V; (5)VIN, Input Voltage: –0.5V to +7.0V; (6)IIN, Input Current: –30mA to +5.0mA; (7)VO, Voltage Applied to Any Output: Disabled or Power-Off State: –0.5V to 5.5V; HIGH State: -0.5V to VCC; (8)Current Applied to Output in LOW State (Max.): twice the rated IOL(mA); (9)DC Latchup Source Current: –500mA; (10)Over Voltage Latchup (I/O): 10V.

Features

74ABT573CPC features: (1)Inputs and outputs on opposite sides of package allow easy interface with microprocessors; (2)Useful as input or output port for microprocessors; (3)Functionally identical to ABT373; (4)3-STATE outputs for bus interfacing; (5)Output sink capability of 64mA, source capability of 32mA; (6)Guaranteed output skew; (7)Guaranteed multiple output switching specifications; (8)Output switching specified for both 50pF and 250pF loads; (9)Guaranteed simultaneous switching, noise level anddynamic threshold performance; (10)Guaranteed latchup protection; (11)High-impedance, glitch-free bus loading during entire power up and power down; (12)Nondestructive, hot insertion capability.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74ABT573CPC |

Fairchild Semiconductor |

Latches Octal D-Type Latch |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

74ABT00 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74ABT00D,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-IN NAND GATE |

Data Sheet |

|

|

||||||||||||

|

74ABT00D,118 |

|

IC 2-IN GATE NAND QUAD 14SOIC |

Data Sheet |

|

|

||||||||||||

|

74ABT00DB,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

|

74ABT00DB,118 |

|

IC 2-IN GATE NAND QUAD 14-SSOP |

Data Sheet |

|

|

||||||||||||

|

74ABT00N,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))