Product Summary

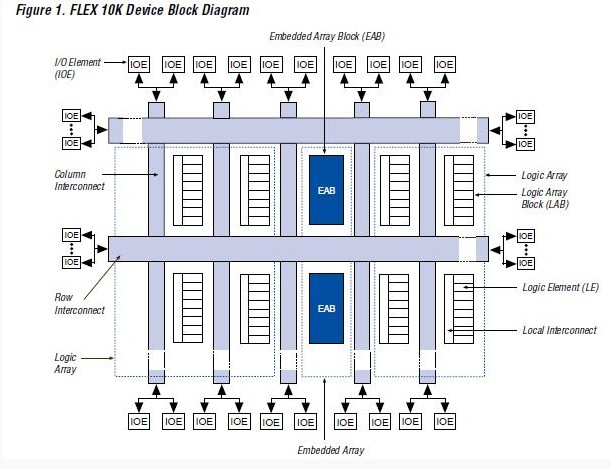

The EPF10K30AQC208-2 device is an industry first embedded PLD. Based on reconfigurable CMOS SRAM elements, the Flexible Logic Element MatriX (FLEX) architecture incorporates all features necessary to implement common gate array megafunctions. With up to 250,000 gates, the EPF10K30AQC208-2 provides the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device.

Parametrics

EPF10K30AQC208-2 absolute maximum ratings: (1)Supply voltage With respect to ground (2): –2.0 to 7.0 V; (2)DC input voltage: –2.0 to 7.0 V; (3)DC output current, per pin: –25 to 25 mA; (4)Storage temperature No bias: –65 to 150℃; (5)Ambient temperature Under bias: –65 to 135℃; (6)Junction temperature Ceramic packages, under bias: 150℃; PQFP, TQFP, RQFP, and BGA packages, under bias, 135℃.

Features

EPF10K30AQC208-2 features: (1)The industry first embedded programmable logic device (PLD) family, providing System-on-a-Programmable-Chip (SOPC) integration; (2)High density; (3)System-level features; (4)Flexible interconnect; (5)Powerful I/O pins; (6)Peripheral register for fast setup and clock-to-output delay; (7)Flexible package options.

Diagrams

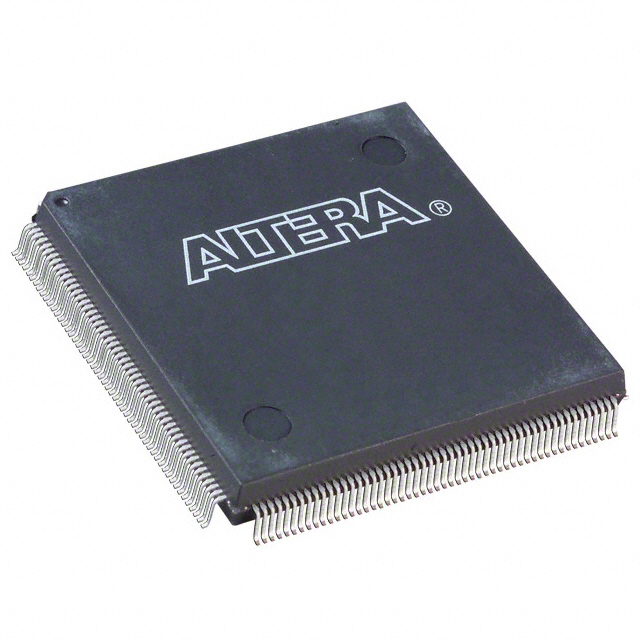

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EPF10K30AQC208-2 |

|

IC FLEX 10KA FPGA 30K 208-PQFP |

Data Sheet |

|

|

||||||

|

EPF10K30AQC208-2N |

|

IC FLEX 10KA FPGA 30K 208-PQFP |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))