Product Summary

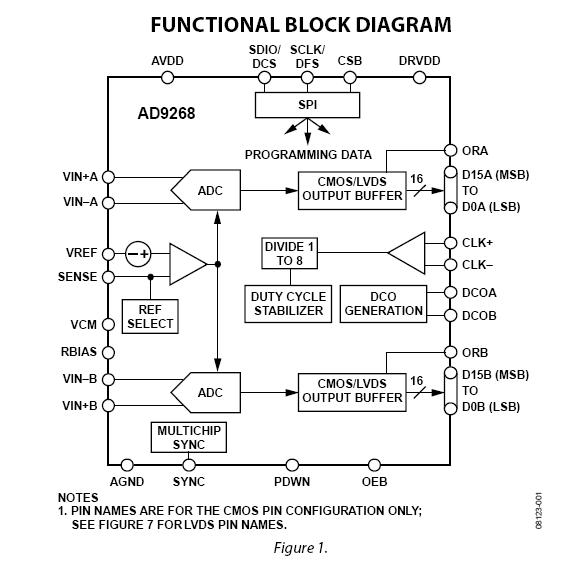

The AD9268BCPZ-105 is a dual, 16-bit, 80 MSPS/105 MSPS/125 MSPS analog-to-digital converter (ADC). The AD9268BCPZ-105 is designed to support communications applications where high performance, combined with low cost, small size, and versatility, is desired. The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth, differential sample-and-hold analog input amplifiers that support a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance. The applications of the AD9268BCPZ-105 include Communications, Diversity radio systems, Multimode digital receivers (3G) GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA, I/Q demodulation systems, Smart antenna systems, General-purpose software radios, Broadband data applications, Ultrasound equipment.

Parametrics

AD9268BCPZ-105 absolute maximum ratings: (1)AVDD to AGND: -0.3 V to +2.0 V; (2)DRVDD to AGND: -0.3 V to +2.0 V; (3)VIN+A/VIN+B, VIN.A/VIN.B to AGND: -0.3 V to AVDD + 0.2 V; (4)CLK+, CLK. to AGND: -0.3 V to AVDD + 0.2 V; (5)SYNC to AGND: -0.3 V to AVDD + 0.2 V; (6)VREF to AGND: -0.3 V to AVDD + 0.2 V; (7)SENSE to AGND: -0.3 V to AVDD + 0.2 V; (8)VCM to AGND: -0.3 V to AVDD + 0.2 V; (9)RBIAS to AGND: -0.3 V to AVDD + 0.2 V; (10)CSB to AGND: -0.3 V to DRVDD + 0.2 V; (11)SCLK/DFS to AGND: -0.3 V to DRVDD + 0.2 V; (12)SDIO/DCS to AGND: -0.3 V to DRVDD + 0.2 V; (13)OEB: -0.3 V to DRVDD + 0.2 V; (14)PDWN: -0.3 V to DRVDD + 0.2 V; (15)D0A/D0B through D15A/D15B to AGND: -0.3 V to DRVDD + 0.2 V; (16)DCOA/DCOB to AGND: -0.3 V to DRVDD + 0.2 V; (17)Operating Temperature Range (Ambient): -40℃ to +85℃; (18)Maximum Junction Temperature Under Bias: 150℃; (19)Storage Temperature Range (Ambient): -65℃ to +150℃.

Features

AD9268BCPZ-105 features: (1)SNR = 78.2 dBFS @ 70 MHz and 125 MSPS; (2)SFDR = 88 dBc @ 70 MHz and 125 MSPS; (3)Low power: 750 mW @ 125 MSPS; (4)1.8 V analog supply operation; (5)1.8 V CMOS or LVDS output supply; (6)Integer 1-to-8 input clock divider; (7)IF sampling frequencies to 300 MHz; (8)-153.6 dBm/Hz small-signal input noise with 200Ω input impedance @ 70 MHz and 125 MSPS; (9)Optional on-chip dither; (10)Programmable internal ADC voltage reference; (11)Integrated ADC sample-and-hold inputs; (12)Flexible analog input range: 1 V p-p to 2 V p-p; (13)Differential analog inputs with 650 MHz bandwidth; (14)ADC clock duty cycle stabilizer; (15)95 dB channel isolation/crosstalk; (16)Serial port control; (17)User-configurable, built-in self-test (BIST) capability; (18)Energy-saving power-down modes.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

AD9268BCPZ-105 |

|

IC ADC 16BIT 105MSPS DL 64LFCSP |

Data Sheet |

|

|

||||||||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||||

|

AD9200 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||

|

AD9200ARS |

|

IC ADC CMOS 10BIT 20MSPS 28-SSOP |

Data Sheet |

|

|

||||||||||||||||||

|

AD9200ARSRL |

|

IC ADC 10BIT CMOS 20MSPS 28-SSOP |

Data Sheet |

|

|

||||||||||||||||||

|

AD9200ARSZ |

|

IC ADC 10BIT CMOS 20MSPS 28-SSOP |

Data Sheet |

|

|

||||||||||||||||||

|

AD9200ARSZRL |

|

IC ADC 10BIT CMOS 20MSPS 28-SSOP |

Data Sheet |

|

|

||||||||||||||||||

|

AD9200JRS |

Analog Devices Inc |

IC ADC 10BIT CMOS 20MSPS 28-SSOP |

Data Sheet |

|

|

||||||||||||||||||

(China (Mainland))

(China (Mainland))