Product Summary

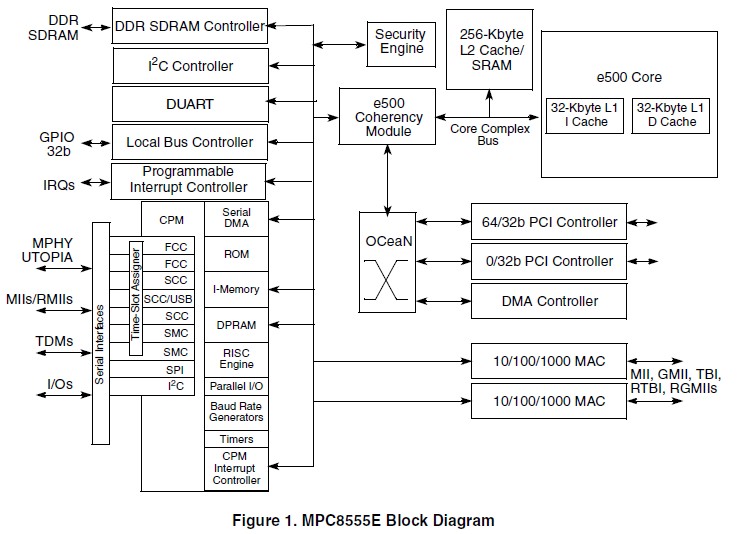

The MPC8555EVTAJD PowerQUICC III Integrated Communications Processor integrates a PowerPC processor core built on Power Architecture technology with system logic required for networking, telecommunications, and wireless infrastructure applications. The MPC8555EVTAJD is a member of the PowerQUICC III family of devices that combine system-level support for industry-standard interfaces with processors that implement the embedded category of the Power Architecture technology.

Parametrics

MPC8555EVTAJD absolute maximum ratings: (1)Core supply voltage, VDD: –0.3 to 1.32, 0.3 to 1.43 (for 1 GHz only) V; (2)PLL supply voltage, AVDD: –0.3 to 1.32, 0.3 to 1.43 (for 1 GHz only)V; (3)DDR DRAM I/O voltage, GVDD: –0.3 to 3.63 V; (4)Three-speed Ethernet I/O, MII management voltage, LVDD: –0.3 to 3.63, –0.3 to 2.75V; (5)CPM, PCI, local bus, DUART, system control and power management, I2C, and JTAG I/O voltage, OVDD: –0.3 to 3.63 V; (6)Input voltage, DDR DRAM signals, MVIN: –0.3 to (GVDD + 0.3) V; (7)DDR DRAM reference, MVREF: –0.3 to (GVDD + 0.3) V; (8)Three-speed Ethernet signals, LVIN: –0.3 to (LVDD + 0.3) V; (9)CPM, Local bus, DUART, SYSCLK, system control and power management, I2C, and JTAG signals, OVIN: –0.3 to (OVDD + 0.3)1 V; (10)PCI ,OVIN: –0.3 to (OVDD + 0.3) V; (11)Storage temperature range, TSTG: –55 to 150 ℃.

Features

MPC8555EVTAJD features: (1)High-performance, 32-bit Book E-enhanced core that implements the PowerPC architecture; (2)Dual-issue superscalar, 7-stage pipeline design; (3)32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection; (4)Lockable L1 caches-entire cache or on a per-line basis; (5)Separate locking for instructions and data; (6)Single-precision floating-point operations; (7)Memory management unit especially designed for embedded applications; (8)Enhanced hardware and software debug support; (9)Dynamic power management; (10)Performance monitor facility; (11)Uses JTAG interface and a TAP controller to access entire system memory map; (12)Supports 32-bit accesses to configuration registers; (13)Supports cache-line burst accesses to main memory; (14)Supports large block (4-Kbyte) uploads and downloads; (15)Supports continuous bit streaming of entire block for fast upload and download; (16)IEEE Std 1149.1-compatible, JTAG boundary scan; (17)783 FC-PBGA package.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

MPC8555EVTAJD |

Freescale Semiconductor |

Microprocessors (MPU) PQ 37 LITE 8555E |

Data Sheet |

|

|

||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||

|

MPC800 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

MPC801 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

MPC801KG |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

mPC8104GR |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

mPC8106TB |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

mPC8109TB |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

(China (Mainland))

(China (Mainland))